FAST入门(5)FAST硬件流水線(xiàn)之一

发布时间:2018-07-12

FPGA中实现的硬件流水線(xiàn)是FAST平台实现分(fēn)组硬件处理(lǐ)的基础。FPGA OS為(wèi)FAST流水線(xiàn)提供了基本的分(fēn)组收发,高速DMA和查表等服務(wù)。FAST 流水線(xiàn)与FPGA OS的接口定义直接反映了分(fēn)组硬件处理(lǐ)功能(néng)在FPGA OS和FAST流水線(xiàn)中的划分(fēn),也是FAST平台提供商(shāng)必须考虑的关键问题。

一、FAST流水線(xiàn)接口定义

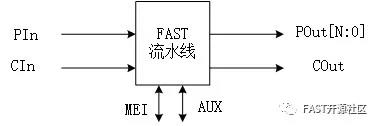

FAST流水線(xiàn)与FPGA OS之间定义了6个接口,分(fēn)别是PIn/POut、CIn/COut,MEI和AUX。如下图所示。

PIn/POut是流水線(xiàn)接收和发送分(fēn)组的接口,CIn/COut分(fēn)别是流水線(xiàn)接收和发送流水線(xiàn)控制信息的接口,MEI(Match Engine Interface)是流水線(xiàn)访问FPGA OS提供的匹配引擎的接口。AUX是FPGA OS為(wèi)FAST流水線(xiàn)提供时钟、复位和时间戳等信息的接口。

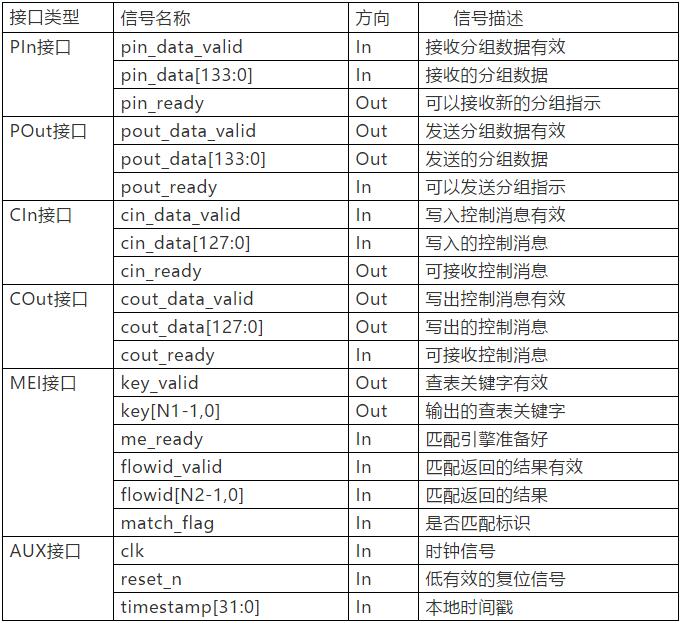

各接口信号的详细定义如下表所示。其中MEI接口中的信号宽度N1/N2与平台相关。Clk时钟频率与平台相关,一般不小(xiǎo)于125MHz。所有(yǒu)I/O信号的变化都与CLK同步。

FAST流水線(xiàn)通过Key接口向查表协处理(lǐ)器提交查表关键字,从FlowID接口接收返回的查表结果(匹配的地址)。包括是否匹配(match_flag為(wèi)1表示匹配,0表示未匹配),以及匹配的规则序号FlowID等。

只要me_ready信号有(yǒu)效,FAST流水線(xiàn)可(kě)连续地向查表协处理(lǐ)器提交查表请求,查表协处理(lǐ)器必须保证这些查表结果按照查表请求提交的顺序返回查表结果。

查表协处理(lǐ)器中规则的配置管理(lǐ)方法与具體(tǐ)的平台相关。FAST库在实现时必须对不同的平台进行适配,提供管理(lǐ)这些规则的API接口。

二、数据通路PIn/POut数据格式

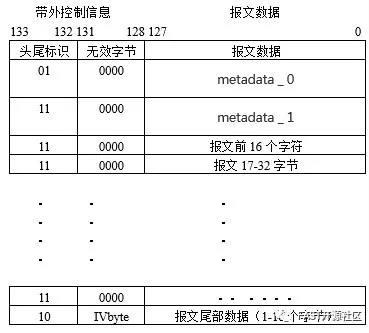

PIn和POut两个接口采用(yòng)相同的分(fēn)组格式,分(fēn)组数据宽度為(wèi)134位,其中低128位為(wèi)报文(wén)数据,高6位為(wèi)控制信息,每个数据分(fēn)组包括32字节的metadata和分(fēn)组数据,如下图所示。

分(fēn)组数据的格式為(wèi)接口收发的以太网报文(wén)格式。其中以太网报文(wén)格式中不包含最后的4字节CRC字段,接收时,FPGA OS负责接收时进行CRC校验和剥离,发送时,FPGA OS会计算分(fēn)组的CRC字段并附加在报文(wén)最后。

数据通路的[133:132]位為(wèi)报文(wén)数据的头尾标识。01标识报文(wén)头部,11标识报文(wén)中间数据,10标识报文(wén)尾部。由于不同报文(wén)具有(yǒu)不同長(cháng)度,因此在报文(wén)数据最后一拍可(kě)能(néng)存在一些无效的字节。数据报文(wén)的最后一拍的[131:128]位用(yòng)来标识无效字节的个数。其中0000表示16个字节全部有(yǒu)效;0001标识最低1个字节无效,最高15个字节有(yǒu)效;以此类推,1111表示最低15个字节无效,最高1个字节有(yǒu)效。

设FAST流水線(xiàn)的时钟频率為(wèi)xMhz,因此数据通路理(lǐ)论传输带宽為(wèi)128bit*xMHz。例如当x=125时,通路带宽為(wèi)16Gbps。

三、控制通路CIn/COut数据格式

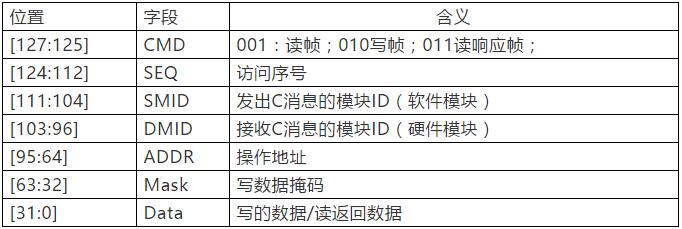

FAST流水線(xiàn)的控制通路CIn和COut采用(yòng)相同的消息格式。对FAST流水線(xiàn)模块的每次读写操作都转换成一个128位宽的命令字写入FAST流水線(xiàn)。命令字的格式如下表所示。与流水線(xiàn)处理(lǐ)分(fēn)组信息一样,每个模块只处理(lǐ)DMID等于本地模块号的命令字。相应的模块完成读写操作后,修改命令字,并将命令字发送给下游模块,最后命令字从COut接口输出。FPGA OS负责将软件读写请求转换成FAST流水線(xiàn)的命令字,并将COut输出的命令字返回给由SMID标识的软件模块。

显然,每个硬件模块内部的编址与都是32位,且编址方法与其他(tā)模块无关,由模块开发者独立确定。