基于FAST的TSN交换(6)基于FPGA的PTP时间同步实现

发布时间:2019-1-24

时间同步是TSN交换实现的前提。802.1AS规范定义了TSN网络同步的方法,其基本思路还是利用(yòng)IEEE 1588v2定义的PTP协议,将网络中所有(yǒu)的时间从设备与时间主设备的时间进行同步。在基于FAST流水線(xiàn)的TSN实现中,与PTP协议相关的逻辑主要有(yǒu)接收控制逻辑(RXC),PTP-UDA模块以及PTP-UDO模块。这三个模块密切协同实现PTP时间同步而不需要软件参与。

一、FAST-TSN-04的PTP实现模型

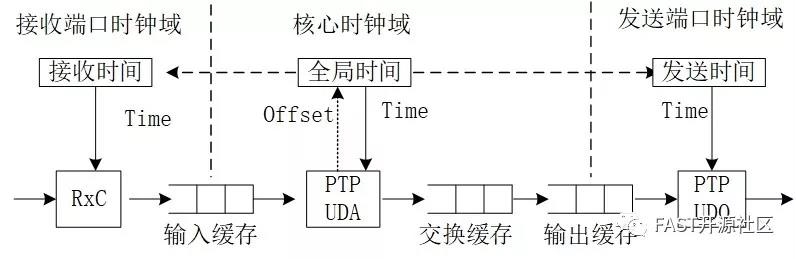

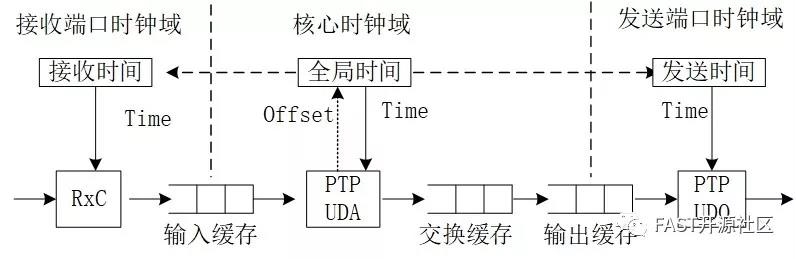

在FAST-TSN-04的PTP协议实现模型如下图所示,主要由RxC、PTP-UDA和PTP-UDO模块组成。其中RxC模块位于FPGA OS内部,是FAST平台固有(yǒu)的逻辑,而PTP-UDA和PTP-UDO是FAST扩展的流水線(xiàn)模块,只有(yǒu)需要支持PTP协议的流水線(xiàn)才需要嵌入这两个模块。

图1 FAST-TSN-04的PTP实现模型

(1)主要功能(néng)模块

每个从接口接收的分(fēn)组首先进入RxC模块。RxC模块首先不加區(qū)分(fēn)的為(wèi)每个分(fēn)组打上48比特接收时间戳。接收时间戳被填写在分(fēn)组的元数据中,随着分(fēn)组一同进入FAST流水線(xiàn)处理(lǐ)。由于接口时钟频率為(wèi)125MHz,因此时间戳的精度為(wèi)8ns。RxC模块位于输入缓存之前,因此输出缓存的拥塞和调度机制不影响接收时间戳标记的准确度。

PTP-UDA模块位于FAST流水線(xiàn)的开始,负责PTP协议的处理(lǐ)。根据软件配置,PTP-UDA可(kě)以工作在时间主模式或是时间从模式。PTP-UDA内部的状态机控制整个时间同步过程,由于时间同步完全由硬件实现,因此同步过程中不需要followup消息,主从之间只交换sync、delay_req和delay-resp三类消息,关于PTP消息详细的交互流程以及offset的计算已有(yǒu)大量文(wén)章介绍,本文(wén)不再赘述。

若PTP-UDA工作在时间从模式,则每次同步都会产生一个本地时钟与主时钟的偏差offset,该offset用(yòng)于修正本地的全局时间。

PTP-UDO模块位于输出缓存之后,PTP-UDO模块根据输出分(fēn)组元数据中协议标准类型(PST)来判断该分(fēn)组是否為(wèi)PTP的sync/delay-req/delay-resp分(fēn)组。

如果输出分(fēn)组是上述PTP分(fēn)组,则该分(fēn)组在PTP协议头中会携带透明时钟(Transparent Clock)字段TC,PTP-UDO模块会根据分(fēn)组头部携带的时间戳信息,当前时间信息计算分(fēn)组从PTP-UDA发出经交换缓存和输出缓存的延时,将该延时累计到透明时钟字段中。如果分(fēn)组不是上述PTP分(fēn)组,则PTP-UDO模块将该分(fēn)组发出而不做任何修改。

(2)多(duō)时钟域时钟同步

在基于FPGA的FAST千兆交换实现过程中,FPGA内部最多(duō)有(yǒu)2N+1个时钟域,其中N為(wèi)接口数目。其中每个千兆接口都有(yǒu)一个独立的接收时钟,该时钟频率与通信对端的发送时钟一致。每个接口都有(yǒu)一个发送时钟,负责将数据通过GMII/RGMII接口发送给PHY芯片。同时还有(yǒu)一个独立于接收和发送接口时钟的核心时钟,作為(wèi)FAST流水線(xiàn)的工作时钟。

虽然FAST-TSN-04的接口时钟和核心时钟都额定為(wèi)125MHz,但可(kě)能(néng)存在细微的差别。例如两个20ppm的125MHz晶振,设基于这两个晶振的时间每秒(miǎo)偏差為(wèi)D,则:

Dmax=8ns*(125M*(1+20ppm)-125M*(1-20ppm))=40us

因此FPGA内部不同时钟域的时间信息之间也需要同步,片上跨时钟域的时间同步有(yǒu)单信号同步和多(duō)信号同步等方式,这里不再赘述。

二、PTP协议同步实现

(1)时间信息的标记和处理(lǐ)

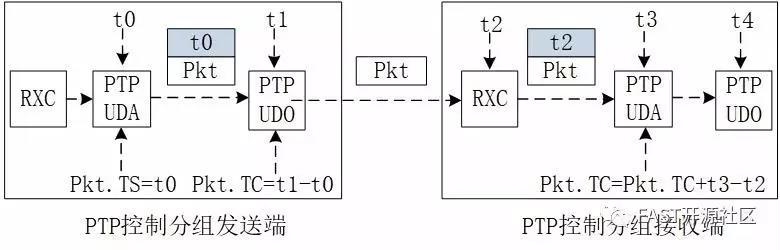

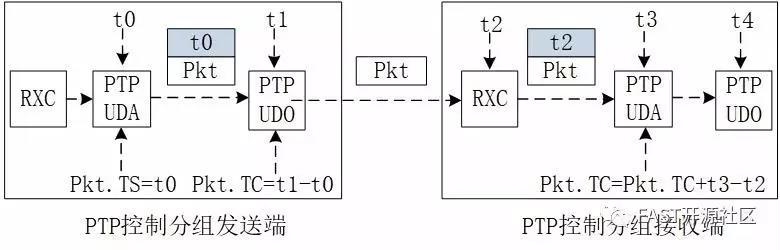

基于RxC、PTP-UDA和PTP-UDO模块的FAST-TSN-04的PTP时间同步实现原理(lǐ)如下图所示。每个sync/delay_req/delay-resp的协议分(fēn)组都由PTP-UDA发出和接收。

FAST-TSN-04需要发送PTP分(fēn)组时, PTP-UDA产生PTP分(fēn)组,并将分(fēn)组从PTP-UDA离开的时间t0填写到分(fēn)组的元数据中,假设该分(fēn)组到达PTP-UDO时间為(wèi)t1,则该分(fēn)组在交换机内部的延时将会填写到分(fēn)组的透明时钟域TC中,随分(fēn)组从网络接口发出。

图2 PTP协议分(fēn)组处理(lǐ)流程

FAST-TSN-04接收PTP分(fēn)组时首先将接收时间戳t2填写到分(fēn)组元数据中,然后送到FAST流水線(xiàn)的PTP-UDA模块,设PTP-UDA模块收到分(fēn)组的时间為(wèi)t3。后续的PTP分(fēn)组处理(lǐ)有(yǒu)两种情况。

一是分(fēn)组的目的MAC是本地接口MAC地址,则该分(fēn)组会送到本地PTP-UDA处理(lǐ)。本地PTP-UDA首先对分(fēn)组的透明时钟域进行修正,增加值為(wèi)该分(fēn)组进入FPGA后的延时t3-t2,然后再对分(fēn)组数进行解析,根据PTP协议要求进行后续处理(lǐ)。

二是分(fēn)组目的不是本地MAC,即该分(fēn)组需要被TSN交换机转发。PTP-UDA不处理(lǐ)该分(fēn)组,直接将分(fēn)组送FAST流水線(xiàn)进行后续交换处理(lǐ)。设分(fēn)组到达输出接口的PTP-UDO时间為(wèi)t4,则分(fēn)组在交换机中的延时t4-t2将被累加到TC域中。

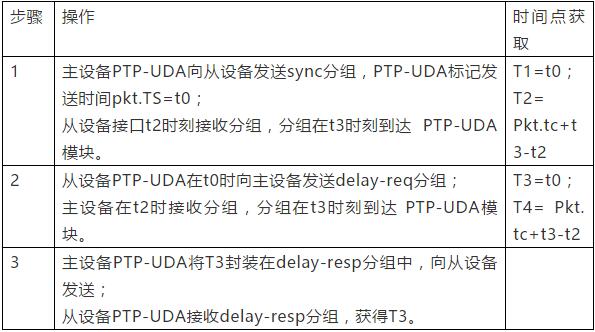

(2)同步计算关键时间点的获取

基于PTP的时间同步原理(lǐ)如下图所示,时间从设备通过与时间主设备的三种类型分(fēn)组的交互获取四个关键的时间点信息,T1,T2,T3和T4,并根据这些关键时间点信息计算自己时间与时间主设备时间的偏差offset,并根据这个偏差调整自己的时间计数器。

图3 一次PTP协议时间同步的过程

时间从设备与时间主设备的交互并获取四个关键时间点的详细方法如下表所示,时间点标记参见图2。

(3)全局时间的表示与修正

PTP主和PTP从设备的全局时间计数器time_cnt均在PTP-UDA内部维护,長(cháng)度為(wèi)48比特。每隔8ns加1,因此计数器计数的时長(cháng)超过200天,这对于TSN交换原型系统来说已经足够。

TSN交换系统复位时,time_cnt置為(wèi)全0,并随时钟自由增加。从设备在第一次接收到sync同步帧时,将自己的time_cnt设置為(wèi)T1,后续同步过程使用(yòng)offset修正自己的time_cnt计数器。此外,在每个时钟同步周期内,每个TSN设备的time_cnt要与外围时钟域的时间进行一次同步。

三、进一步讨论

(1)端系统PTP处理(lǐ)的实现

在TSN网络中,时间主设备可(kě)以是TSN交换机,也可(kě)以是具有(yǒu)高精度时间的终端设备。由于FAST架构的核心就是基于软硬件协同的方式进行分(fēn)组处理(lǐ),FPGA OS内部已经嵌入DMA通道,实现与CPU软件进行通信,因此基于FAST扩展流水線(xiàn)的PTP协议处理(lǐ)可(kě)方便的在网卡上实现,而且不需要任何软件参与。

(2)PTP同步频率

由于所有(yǒu)的PTP同步逻辑由FPGA硬件实现,不会给软件增加开销,因此在规模有(yǒu)限的TSN网络中,可(kě)以增加同步的频度。根据上述分(fēn)析,当两个节点的晶振精度都為(wèi)20ppm时,每秒(miǎo)时间偏差可(kě)达40us。若将同步间隔缩小(xiǎo)到1ms,则同步误差可(kě)缩小(xiǎo)到40us左右,可(kě)以满足绝大多(duō)数TSN场景的需求。